Parallel Input Serial Output Shift Register Verilog Code

Verilog Code for Parallel in Parallel Out Shift Register - Free download as Word Doc (.doc /.docx), PDF File (.pdf), Text File (.txt) or read online for free. Scribd is the world's largest social reading and publishing site.

Library IEEE; use IEEE.STD_LOGIC_1164. ALL; use IEEE.STD_LOGIC_ARITH.

Lana del rey lust for life. Evaluasi media pembelajaran pdf. ALL; use IEEE.STD_LOGIC_UNSIGNED. ALL; entity P2S is port ( Serial_out: out std_logic; clk: in std_logic; Parallel_data: in std_logic_vector( 15 downto 0); DataReady: in std_logic); end P2S; architecture Behavioral of P2S is signal OldReady: std_logic:= '0'; signal Shreg: std_logic_vector( 15 downto 0); begin process (clk) begin if (clk 'event and clk = '1') then Shreg.

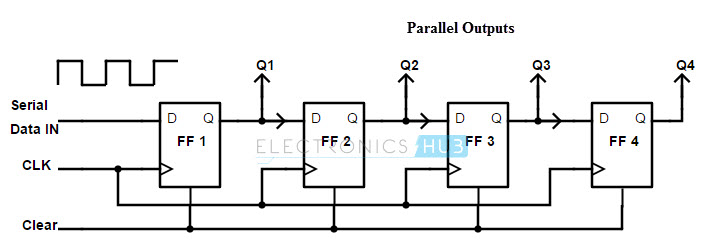

Parallel Input Serial Output Shift Registers

Ya input is fixed length of 16 bit but this parallel to serial converter logic should be programmable when ever the data will arrive then dat should get serialized. For example 1st i got the data of 6 bit length at that time that data should be latched then it should get serialized. Similarly some other time when i get the data of length10 bit even in same way that should get serialized. This means our logic should be 1 time programmed instead of runtime programmable. I think u got my point. > For example 1st i got the data of 6 bit length at > that time that data should be latched then it should get serialized. > Similarly some other time when i get the data of length10 bit even in > same way that should get serialized.